3D-Prozesstechnologie für innovative System-in-Package (3D-SiP)-Anwendungen

Die Integrationsdichte elektronischer Komponenten ist ein Schlüsselelement in der Produktentwicklung. Die notwendige Reduktion der Strukturgrößen ist jedoch durch technische Grenzen und steigende Kosten limitiert. Das dreidimensionale Stacking von Chips, kombiniert mit der Prozessierung auf Waferebene, erlaubt eine funktionale Erweiterung und Erhöhung der Komplexität von elektronischen Systemen auf kleinstem Raum.

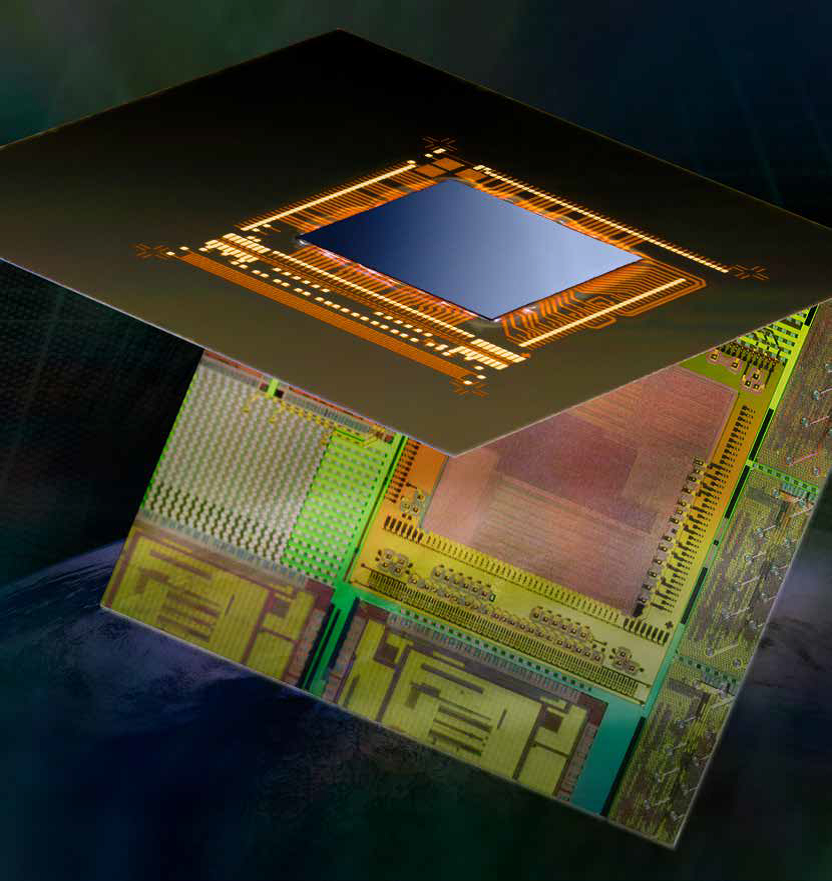

Ziel des EU-Verbundprojekts Master_3D war die Etablierung einer integrierten Plattform (Anlagen, Materialien, Prozesse) für die Realisierung dreidimensionaler innovativer System-in-Package (3D-SiP)-Lösungen. Damit wurden Methoden und Technologien für höchste Kontaktdichten, dünne Siliziumintegration sowie neue Analytik- und Testverfahren mit der Zielsetzung entwickelt, die konventionelle Aufbau- und Verbindungstechnik auf Waferebene und in die dritte Dimension zu erweitern, insbesondere unter Berücksichtigung von Zuverlässigkeit, Leistungsfähigkeit und Prozessmonitoring. Der Institutsteil IZM-ASSID hat im Projekt wesentliche Ergebnisse bei der Entwicklung und Performanceverbesserung von für die 3D-Integration technologisch wichtigen Einzelprozessen erreicht. In Zusammenarbeit mit den Industriepartnern wurden an Anwendungsbeispielen kritische Prozessschritte bezüglich der Produktanforderung analysiert und bewertet, Samples mit relevanten 3D-Strukturen für die Prozesstool- und Analysetoolhersteller geschaffen und die Neuerungen gemeinsam evaluiert und validiert.

Auf der Technologielinie des IZM-ASSID wurden die Ergebnisse aus dem Projekt in applikationsgetriebenen 3D-Demonstratoren für die Projektpartner NXP und Infineon angewendet. So stellt der NXP-Demonstrator eine Sicherheitsschaltung mit NFC-Interface (Near Field Communication) dar, in dem mittels 3D-Integration ein zusätzliches Sicherheits-Feature integriert und damit das Sicherheits-Level erhöht wurde.

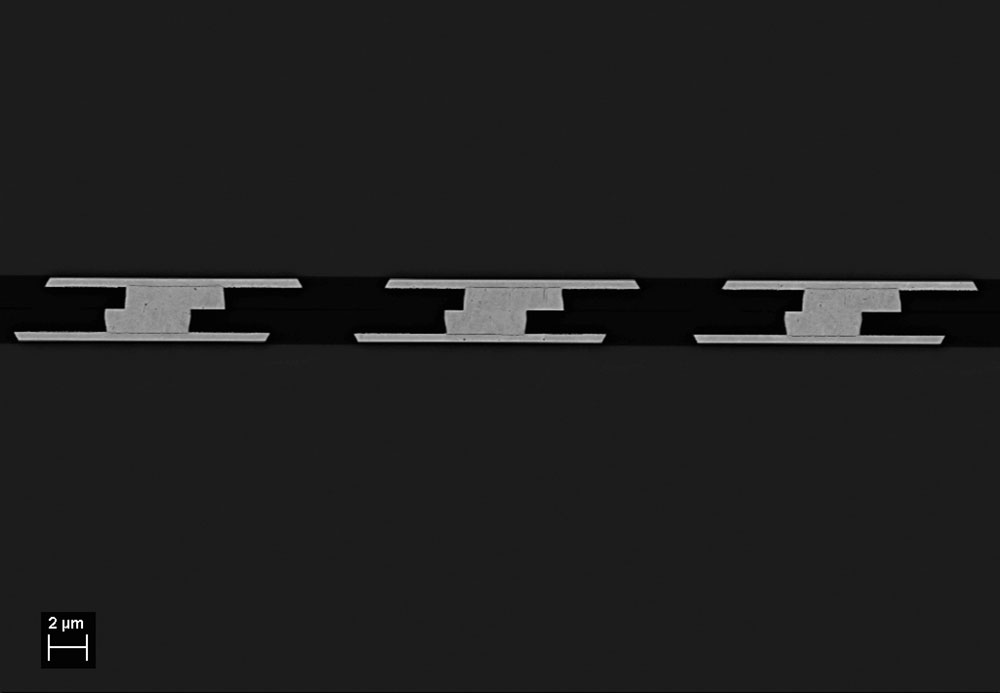

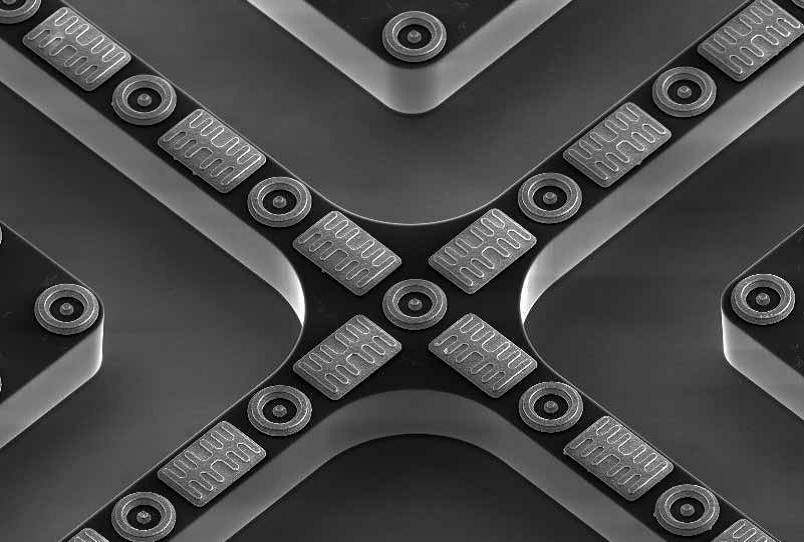

Ein erweitertes Verständnis der Interaktion von Einzelprozessen und deren Auswirkungen auf die elektrische Leistungsfähigkeit konnte mit zahlreichen, teils neu entwickelten dedizierten 3D-Teststrukturen erreicht werden, die zum Teil in Interaktion mit den aktiven Komponenten des NXP-CMOS-Wafers agieren. In Kombination mit der Etablierung eines neuen Testablaufs konnten so für jedes 3D-Prozessmodul elektrische Daten gesammelt und Prozesseinflüsse auf das jeweilige Prozessmodul korreliert werden. Weiterhin wurde ein neues Konzept zur Integration von TSVs als Transistor-Gate in MOS-Transistoren initial erfolgreich getestet (vertikaler N- und P-MOS-Transistor).

Fraunhofer Dresden

Fraunhofer Dresden